Achievements & Impact

Research & Projects

Our current focus areas:

- Low-power RISC-V SoC design for embedded/IoT applications.

- AI/ML accelerator architectures on FPGA for edge computing.

- Secure microcontroller and hardware security research.

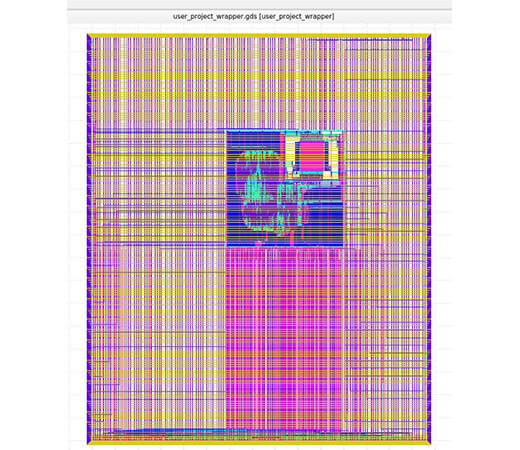

Azadi System on Chip (SoC)

System on Chips

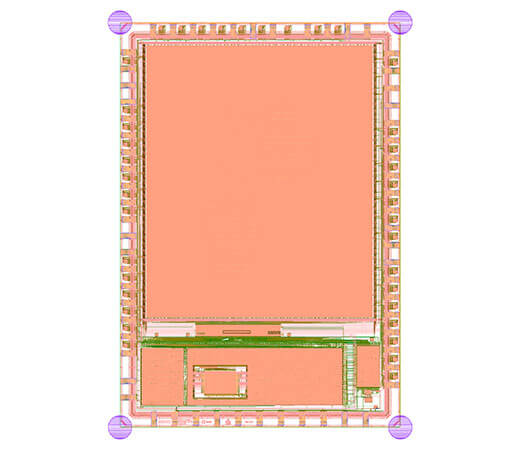

Azadi - آزادی means "The Freedom", this System on a Chip (SoC) is the start of many RISC-V based SoCs to come. It is the Final Year Project (FYP) of our MERL Research Interns i.e Zeeshan Rafique, Sajjad Ahmed, Muhammad Waleed Waseem and Usman Zain ul Abideen as a part of their Bachelor's Degree requirement. Azadi is an SoC with a 32-bit RISC-V signal core extended version of ibex we named it "buraq", it is a 3-stage pipeline core that implements the RV32IMFDC instruction set architecture, a limited number of peripherals UART, SPI, GPIO, PWM, and timer. It also contains a Software Development Kit (SDK) for rapid development, debugging and testing.

LLVM for Vector Extension

Compilers

We are preparing to move forward after the tape-out of the SoCs. We aim to add another extension known as the Vector Extension (short:' V') to our core. This will accelerate our processing speed for complex machine algorithm. We hoped that a low-level virtual machine (LLVM) will provide the opportunity for us to write an inline vector extension assembly. We are forming a team that is solely exploring an LLVM. Another work that is in progress is the optimization of CHISEL generated Verilog which is generated by FIRRTL. Usually, the CHISEL generated Verilog is not much readable the naming convention is not understandable by the observer so for tackling this problem the subset of the students is working on that.

Reverse Engineering Rocket Chip

SoC Generators

Rocket chip is the SoC generator written in Chisel and understood by quite a few. We make our own pedagogy which enabled our undergraduate students to understand this complex and powerful tool and its architecture which is not well documented and is a pain problem for many industries looking to adopt Chisel and RISC-V. Our goal is to Reverse Engineer the Rocket Chip generator by using the expertise of Scala (functional Programming and Object Oriented Programming).

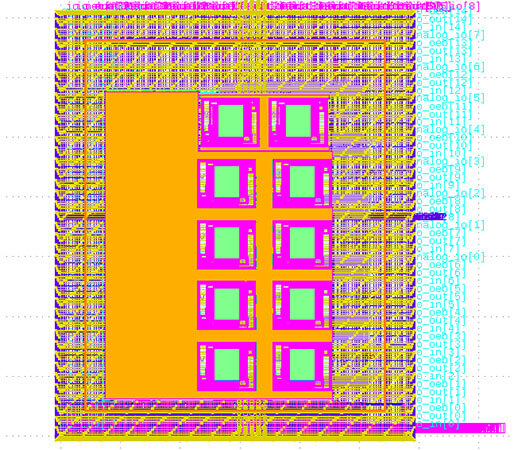

Ibtida System on Chip (SoC)

System on Chips

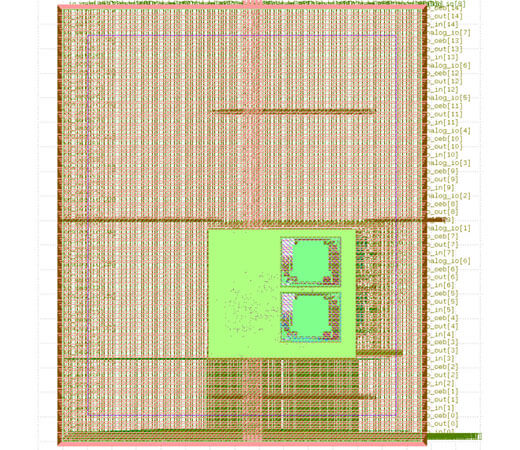

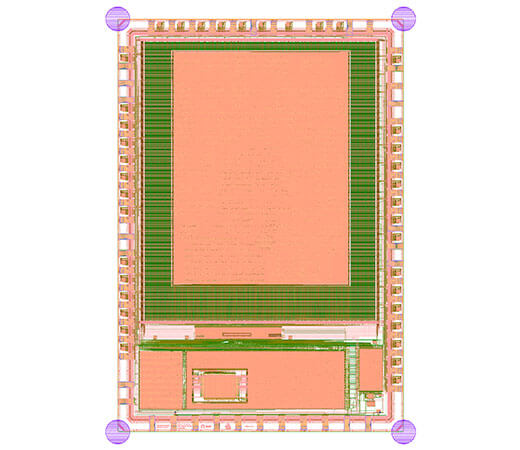

This team is working on the design of a complete System on a Chip (SoC) that is built from scratch based on the RISC-V Instruction Set Architecture (ISA). The Ibtida ابتدا project's aim is to build a completely open-source chip from scratch and take it from designing to fabrication using all open-source tools and Process Design Kit (PDK) made possible by Efabless, Google and FOSSI Foundation.

Ghazi System on Chip (SoC)

System on Chips

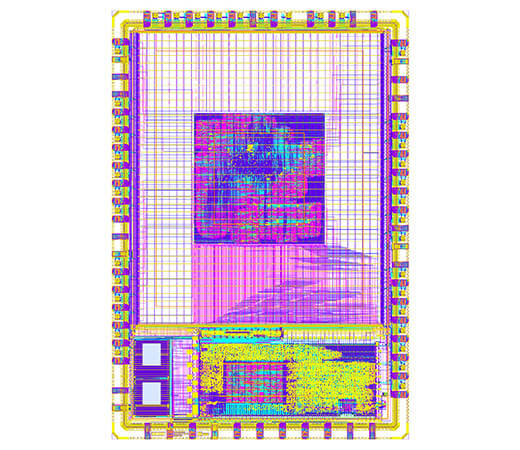

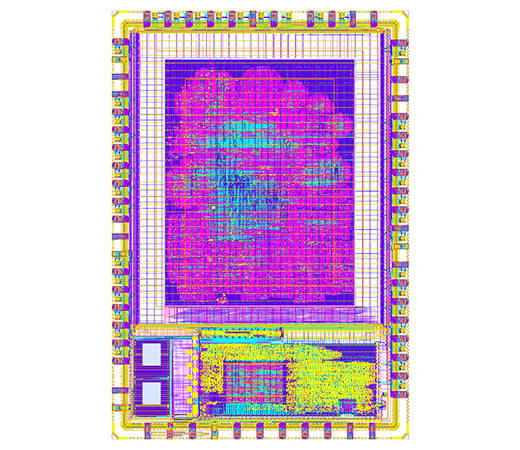

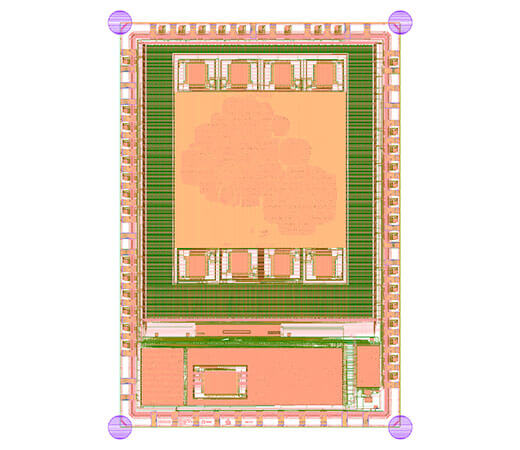

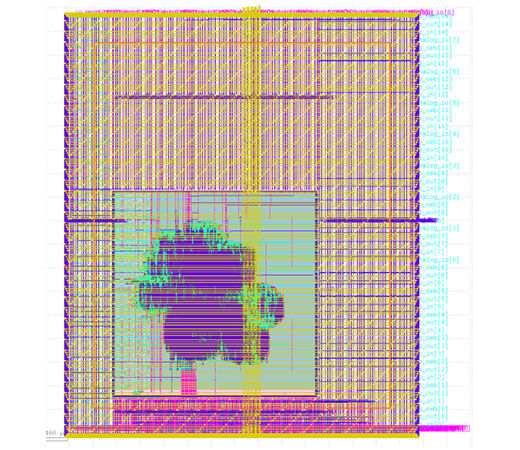

The team behind the RTL (Register Transfer Level), APR (Placement and Routing) and both Pre and Post Synthesis Verification of Ghazi System on a Chip. Uses of a core in deeply embedded systems such as IoT end-nodes range from simple control and interaction with peripherals, to the execution of light-weight processing, all the way up to the computation of complex signal processing algorithms. Design of such cores usually involves high royalty fee and copyright implications when using ARM or Intel x86 based architecture. Thus, an SoC, that uses a core based on an open source ISA (Instruction Set Architecture) is often required that we could easily adapt to suit multiple specifications as needed.

BURQ IDE

Verification

Verification and validation of any hardware is an essential and most important part. For the verification of our SoC we have designed a tool which is known as ‘BURQ’. The idea is that a core (either written in chisel or verilog) could be tested via the IDE automatically without setting up custom compilers or setting paths to the test file and writing scripts.

Oxygen Simulator

Simulators

Oxygen is a student-focused, open-source, educational, and web-based RISC-V Instruction Set Simulator. Oxygen supports I-Extension, IM-Extension and IMC-Extension together. Oxygen was mainly built for education purposes so that the students who want to learn about the RISC-V Instruction Set Architecture can benefit from it

Collaborations & Partnerships

We are proud to partner with:

Events & News

MERL hosts seminars, workshops, training sessions and student showcases to keep the community engaged and active.

Ready to Collaborate or Explore Research Opportunities?

Join us in advancing innovation in Chip Design, VLSI, and Embedded Systems.

Let’s build the future together.